ムーアの法則

原文と比べた結果、この記事には多数の(または内容の大部分に影響ある)誤訳があることが判明しています。情報の利用には注意してください。 (2016年5月) |

ムーアの法則(ムーアのほうそく、英: Moore's law)とは、大規模集積回路(LSI IC)の製造・生産における長期傾向について論じた1つの指標であり、経験則に類する将来予測である。

発表当時フェアチャイルドセミコンダクターに所属しており後に米インテル社の創業者のひとりとなるゴードン・ムーアが1965年に自らの論文上に示したのが最初であり、その後、関連産業界を中心に広まった[1]。

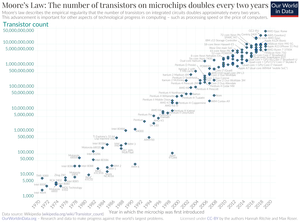

彼は1965年に、集積回路あたりの部品数が毎年2倍になると予測し、この成長率は少なくともあと10年は続くと予測した。1975年には、次の10年を見据えて、2年ごとに2倍になるという予測に修正した。彼のこの2年ごとに2倍になるとの予測は1975年以降も維持され、それ以来「ムーアの法則」として知られるようになった。

初出

[編集]ムーアの元々の文章は以下である。

(原文) The complexity for minimum component costs has increased at a rate of roughly a factor of two per year (see graph on next page). Certainly over the short term this rate can be expected to continue, if not to increase. Over the longer term, the rate of increase is a bit more uncertain, although there is no reason to believe it will not remain nearly constant for at least 10 years. That means by 1975, the number of components per integrated circuit for minimum cost will be 65,000.

I believe that such a large circuit can be built on a single wafer.

"Cramming more components onto integrated circuits", Electronics Magazine 19 April 1965[2]

(訳)部品あたりのコストが最小になるような複雑さは、毎年およそ2倍の割合で増大してきた((訳注)元文献ではここでグラフを参照している)。短期的には、この増加率が上昇しないまでも、現状を維持することは確実である。より長期的には、増加率はやや不確実であるとはいえ、少なくとも今後10年間ほぼ一定の率を保てないと信ずべき理由は無い。すなわち、1975年までには、最小コストで得られる集積回路の部品数は65,000に達するであろう。

私は、それほどにも大規模な回路が1個のウェハー上に構築できるようになると信じている。

チップの複雑さはトランジスタの個数に比例すると仮定し、それらが何に使われているかを無視するならば、この法則は今日まで充分時の試練に耐えてきたと言える。しかし、トランジスタ当たりの複雑さは、RAMキャッシュでは実行ユニットほど高くないという議論もあり得る。こんにちのマイクロプロセッサの祖である4004も、DRAMの祖である1103も1970年前後に登場したのであり、それらより5年も前に述べられたことでもある(また「1個のウェハー」についても、こんにちの直径300mmのウェハーへの wafer-scale integration のようなものを想定してはいないだろう)。そういった観点からすれば、ムーアの法則の妥当性は、その定式化のしかたによっては疑問符がつくものとなる。ただし、その成長が指数的であるという点に異論は無いと推測される。

なお、1枚のチップ(a chip)に集積される部品数は、プロセスの微細化とチップ面積の拡大の2つの要素の掛け合わせで増加する。

また「ムーアの法則」と名づけたのはムーア自身ではなく、その著書 Introduction to VLSI Systems(『超LSIシステム入門』)などで知られるカーバー・ミードによる[3]。

ムーアは今日の機械式マウスの共同発明者であるダグラス・エンゲルバートから、1960年の講義にて集積回路のサイズ縮小の見通しについて議論したのを聞いた可能性がある[4]。

公式

[編集]ムーアが1975年に修正した法則は、集積回路上のトランジスタ数は「2年ごとに倍になる」というものである。

これを式で表現すると、n年後の倍率 p は、

となる。したがって、2年後には2倍、5年後には5.66倍、7年後には11.3倍、10年後には32倍、15年後には181.0倍、20年後には1024倍ということになる。

さらには、1チップあたりのコストに対するコンピューティングパワーを増加させ続けるものがムーアの法則だとされ、ハードディスクや果てはコンピュータ以外の技術でも指数的な成長をしていればなんであれ、どれもムーアの法則と呼ぶような傾向さえ現れた。

定量的にはともかく、コンピュータの性能という視点からは「トランジスタ数=ゲートやラッチ数の増加により、より複雑なプロセッサが実装できる」「デナード則により、微細化=高速省電力化である」という、ムーアの法則から間接的に発生する複数の要素が関与して、ひたすらに性能向上が進んだ、と定性的には言うことができるのは確かである。

クーメイ(en:Jonathan Koomey)はこれを定量的に捉え直す試みとして、ムーアの法則による微細化にともなう、デナード則による速度向上と省電力化の定式化と、過去のコンピュータの消費エネルギーあたりの計算量の再調査による長期の傾向から、法則性を取り出し「クーメイの法則」とした。クーメイによれば21世紀に入った後ではその値の成長は鈍化している。

鈍化の原因としては、ゲートやラッチの数をより増やしても、それに比例するようにはコンピュータの性能を上げられなくなったこと(ポラックの法則)、また集積回路技術の微細化による電子的な特性ではリーク電流による悪影響のほうが強くなって、省電力性能が上がりにくくなったこと、が言われている。実際に商品のトレンドとしても、2020年現在では、クロック周波数やシングルスレッド性能は伸び悩み、その一方でコア数の増加は進んでいる。

産業牽引力

[編集]集積回路製造の業界用語で、それに関係する生産プロセスに投入される技術を指すプロセステクノロジ(process technologie)という用語がある。以下では、ムーアの法則の本来の適用範囲についてはその用語「プロセステクノロジ」を、逸脱した拡大解釈によるその他の技術などへの外挿の場合は「技術」などの用語を使う。

ムーアの法則は最初は半導体産業でのプロセステクノロジの観察と予測によって生まれたが、今日ではより広く受け入れられ、先進的な工業製品一般における性能向上の1つの予測値や目標値として用いられることがある。

コンピュータ関係の製品や部品を製造する企業にとって、ムーアの法則が暗示する将来予測は無視できない。例えばCPUやハードディスクのような製品を新規に設計・生産する場合には、最初の出荷まで2年から5年ほどの期間を要するため、こういったメーカーは、投資と収益に関する大きな経済的リスクを負うと共に、数年先の市場を予測した製品開発を行わねばならない。製品の陳腐化が早いいくつかの産業では、先行者利益が大きい分だけ市場参入の遅れは大きな損失を負う可能性があるが、逆に、他社が提供できない新規性があり高性能な製品であっても生産コストが高く販売価格が市場に受け入れられなければ、特殊な用途向きの小さな市場にしか得られない可能性があるため、将来予測は重要である。過去の結果から将来を演繹する将来予測は、「自己成就」などと呼ばれる、それを信じる参加者が多いことでより信頼度の高いものとなるという性質があり、「ムーアの法則」はそのような特性も持っている。

「2年ごとに倍になる」という表現は、ムーアの法則が近年の技術の表象的な進み具合をほのめかしている。より短い時間軸で表現されると、ムーアの法則は平均して1週間に0.6%以上半導体産業全体のパフォーマンスを向上させていると言い換えることができる。

将来のトレンド

[編集]

各々初出荷時点での数

2006年第一四半期において、PCのプロセッサは90nmで製造されており、65nmのチップはIntel(Pentium DおよびIntel Core)からのみ出荷されていた。10年前では、チップは500nmで製造されていた。各企業は45nmや30nm、さらにそれ以下の細かさのチップを製造するために起こる複雑な課題を解決するため、ナノテクノロジーを用いて開発を行っている。これらのプロセステクノロジに因って、半導体産業が直面するムーアの法則の限界の到達が延伸することになるだろう(その後、2010年32nmでトランジスタ数約4億個、2015年には14nmを実現)。

2001年頃のコンピュータ業界のロードマップは、ムーアの法則はチップ数世代にわたって継続するであろう、と予測していた。そのロードマップでの計算によると、2011年にチップ上のトランジスタ数は2の100乗個にまで増加するだろう、と予測していた、というわけである。半導体産業のロードマップではマイクロプロセッサのトランジスタ数は3年で2倍になるとしているので、それに従うと10年で2の9乗個になる。

この法則に経済的合理性があるのは、トランジスタ1個あたりのコストが劇的に下がることである。例えばCore i5には13億個のトランジスタがあり、7万個のトランジスタで1ペニーである。

2006年初頭、IBMの研究者らは深紫外光(DUV、193nm)のフォトリソグラフィで、29.9nm幅の回路をプリントするプロセステクノロジを開発したと発表した。当時IBMは、これによってチップ市場は今までのやり方でムーアの法則の予言をこの数年達成し続けることができるだろう、とした。

計算能力を向上させる方法は、単一の命令ストリームを1つの演算部で可能な限り早く処理するだけとは限らず、遅い動作クロックであっても複数の演算部で並列的に処理することでも計算能力を向上できる。一般に動作クロックの上昇は処理性能に寄与するが、発熱もまた増すために、ある程度まで高速化された演算部では処理性能の向上よりも発熱量の増加が上回り、高集積な回路であれば放熱問題に直面して、動作クロックの高速化は現実的でなくなる[注 1]。

ムーアの法則を基にして、ヴァーナー・ヴィンジやブルース・スターリング、レイ・カーツワイルのような有識者が技術的特異点を部分的に推定している。しかしながら、2005年4月13日、ゴードン・ムーア自身が、「ムーアの法則は長くは続かないだろう。なぜなら、トランジスタが原子レベルにまで小さくなり限界に達するからである」とインタビューで述べている。もっとも、横に並べるならば原子の大きさによる限界があるであろう、というのはムーアでなくてもわかることであって、実際に縦方向に並べる研究がさかんに進められている。

(トランジスタの)サイズに関して、我々は基本的な障壁である原子のサイズに到達するであろう。しかし、その向こう側に行くにはまだ2, 3世代ある。そして、我々が見ることができるよりもさらに向こう側がある。我々が基本的な限界に到達するまでにはあと10〜20年ある。そのときまでには10億を超えるトランジスタを搭載するより巨大なチップを作ることができるだろう[5](2005年の発言)。

ムーアの法則を今後も時間軸に沿って維持するには、裏に潜む様々な挑戦なしにはなしえない。集積回路における主要な挑戦のうちの一つは、ナノスケールのトランジスタを用いることで増加する特性のばらつきとリーク電流である。ばらつきとリーク電流の結果、予測可能な設計マージンはより厳しく、加えてスイッチングしていないにもかかわらず、かなりの電力を消費してしまう。リーク電力を削減するように適応的かつ統計的に設計すると、CMOSのサイズを縮小するのには非常に困難である。これらの話題は「Leakage in Nanometer CMOS Technologies」によく取り上げられている。サイズを縮小する際に生じる挑戦には以下のものがある。

- トランジスタ内の寄生抵抗および容量の制御

- 電気配線の抵抗および容量の削減

- ON/OFFの挙動を制御するためにゲートを終端できる適切なトランジスタ電気的特性の維持

- 線端の粗さによる影響の増加

- ドーピングによる変動

- システムレベルでの電力配送

- 電力配送における損失を効果的に制御する熱設計

- システム全体における製造コストを常に引き下げるようなあらゆる挑戦

カーツワイルによる推測

[編集]

カーツワイルの目算は、ムーアの法則が2019年まで継続することにより、将来たった原子2、3個分にしかない幅のトランジスタがもたらされるというものである。もちろん、より高精度なフォトリソグラフィーを用いるやり方によって達成できるが、このことはムーアの法則の終わりを意味するものではないと彼は考えている。

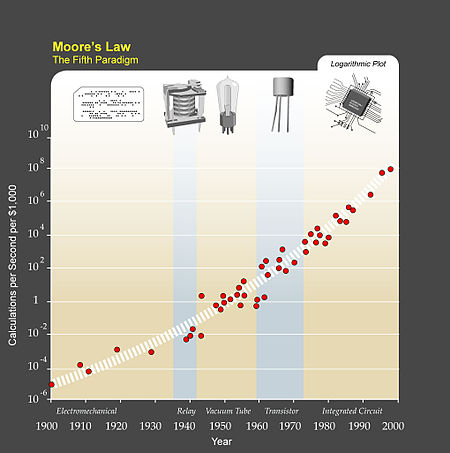

カーツワイルいわく、集積回路におけるムーアの法則は、価格対効果を加速する最初のではなく5番目のパラダイムである。コンピュータは(単位時間当たりの)処理能力はとっくに何倍にもなってきた。1890年にアメリカの国勢調査で使用されたタビュレーティングマシンからLorenz暗号を破るためのMax Newmanのリレー式計算機"Robinson"、アイゼンハワーの選挙予想に使われたCBSの真空管式コンピュータUNIVAC I、最初の宇宙旅行に使われたトランジスタ式コンピュータ、集積回路を用いたPCへと[6]。

カーツワイルは、なんらかの新しい技術が現在の集積回路技術を置き換え、ムーアの法則は2020年以降もずっと長く維持されるのではないか、と推測している。つまり彼は、ムーアの法則に沿った技術の指数関数的な成長は、(ムーアの法則の本来の適用範囲である)プロセステクノロジの発展による集積回路の向上に仮に限界があったとしてもそれを乗り越えて、技術的特異点をもたらすまで、今後も続くであろうと信じているのである。「収穫加速の法則」の中でカーツワイルは、多くの方法によってムーアの法則の一般的な認識は変更されてきたと述べている。ムーアの法則は技術のすべての形を予測すると共通に(しかしそれは誤っているが)信じられている。たとえそれが実際には半導体回路に関してのみ適用されるものとしてもである。多くの未来学者は、いまだカーツワイルによって力を与えられたこれらの考えを述べるために、「ムーアの法則」という言葉を用いている。

その他

[編集]KraussとStarkmanは彼らの論文である「Universal Limits of Computation」で、宇宙に存在するあらゆるシステムの情報処理容量の合計を厳密に見積もった結果、600年という非常に長い期間をムーアの法則の限界と発表した。

この法則は明らかに克服できないように見える障害にしばしば直面したが、すぐにこれらを乗り越えていった。ムーアは、自分が実現した以上に今やこの法則が美しいものに見える、と述べている。「ムーアの法則はマーフィーの法則に違反している。すべてのものはどんどんよくなっていくのだ。」[7]

コスト

[編集]2015年時点で、最新のプロセステクノロジを用いたチップの設計と実用試験には約1億ドルかかった(2005年には1600万ドルだった)。新型チップ製造工場の建設には100億ドルかかった[8]。

法則の限界

[編集]2010年代後半、半導体の開発ペースが鈍化し始め、ムーアの法則のペースが維持できなくなるとの説が広まりだした。2017年5月、NVIDIAのJensen Huangは大手半導体企業のCEOとして初めて、「ムーアの法則は終わった」ことに言及している[9]。

インテル チック・タックは、2006年にインテルが打ち出した戦略で、パターンの大幅な変更無しに新しいプロセステクノロジによって縮小して高性能化した世代のチップと、新しくマイクロアーキテクチャを設計してその前の世代と同じプロセステクノロジで製造するチップとを、毎年交互にリリースする、というもので[10]、ムーアの法則によって2年に1回のペースで新しいプロセステクノロジへの更新があることを前提にしていた。2015年に、この戦略が崩れたことも、現実がムーアの法則通りではなくなっていることのあらわれとみなされている[11]。

2023年現在、ムーアの法則は減速しているが、これは半導体の進歩がネックになっているためである。他の技術の進歩は続いている[要説明][12]。

他の関心事

[編集]コンピュータ関連業界において、ムーアの法則に従って開発が進むのは容量と速度だけではない。RAMの速度とハードディスクのシークタイムは最高年2、3%ずつ改善されている。RAMとハードディスクの容量はそれらの速度と比べて非常に速く増えているので、それらの容量をうまく使うことはますます重要になっている。多くの場合、処理時間とスペースは交換できることがわかっているので、素早いアクセスを行うために何かしらの方法で処理前にインデックスをつけてデータを格納しておく方法などである。コストの点で、より多くのディスクやメモリのスペースが使われる。スペースは時間と比べてより安くなっている。

他方、時々間違えてしまうが、指数関数的なハードウェアの改良は、必ずしもそれと同様な指数関数的なソフトウェアの改良を意味するものではないということである。ソフトウェア開発者の生産性はハードウェアでの進化と共に指数関数的に確実に増えているというわけではなく、たいていの測定では、ゆっくりとまた断続的に増えていく。ソフトウェアは時間と共により大きく複雑になっていく。ヴィルトの法則では「ソフトウェアは、ハードウェアが高速化するより急速に低速化する。」とさえ述べている。

さらに、もっとも有名な間違った考えは、メガヘルツ神話として知られる、プロセッサのクロック速度が処理速度を決定する、というものである。これは実際には、単位時間当たりに処理できる命令数にも依存するので(それぞれの命令の複雑さも同様に依存する)、クロック速度は単に2つの同一の回路同士を比較する時にのみ用いることができる。もちろん、バス幅や周辺回路の速度のような他の要因も考慮に入れなければならない。それゆえに、もっとも有名な「コンピュータの速度」の評価は、原理を理解しなければ元々バイアスがかかっている。これは特にPentiumの時代には真実であった。この時は有名なメーカーが速度の普通の認識として、新製品のクロック速度を宣伝するのに力を入れていた[13]。

たいていのよくある並列化されていないアプリケーションのため、マルチコアCPUのトランジスタ密度は実用的な計算能力に反映して増えているというわけではないことに注意することも重要である。

コンピュータの能力を使用する消費者が負担するコストが落ちているが、ムーアの法則を達成するためのメーカーのコストは逆のトレンドをたどっている。研究開発や製造、テストのコストはチップの世代が新しくなるごとに着実に増えている。半導体メーカーの設備にかかるコストも増え続けると思われるので、メーカーはよりたくさんより大きくて利益の出るチップを売らなければならない(180nmのチップをテープアウトするのにかかるコストは約30万ドルであった。90nmのチップをテープアウトするのにかかるコストは75万ドルを超え、65nmでは100万ドルを超えると思われる)。近年、アナリストたちは先進的なプロセス(0.13μmやそれ以下)で「設計開始」された数が減っているのを目の当たりにしている。2000年以降の景気の低迷の間これらのことが観察されたが、開発の衰退は、長い間世界市場にいた伝統的な半導体メーカーが、経営的にムーアの法則を維持できなくなっていることの証拠であるかもしれない。

しかし、2005年のインテルの報告書では、経営的に安定させながらシリコンチップをダウンサイジングすることは次の十年可能である、としている[14]。シリコン以外の材料を使用することが増えるとのインテルの予想は2006年中ごろには確かめられ、2009年までにはトライ・ゲート・トランジスタを使用するつもりであるとしている。IBMとジョージア工科大学の研究者らは、ヘリウムで極低温まで冷却したシリコン / ゲルマニウムチップを500GHzで動作させ、新しい動作記録速度を作った[15]。チップは4.5K(摂氏マイナス268.65度)で500GHz以上で動作し[16]、シミュレーションの結果では恐らく1THz(1000GHz)で動作することも可能であるとしている。

脚注

[編集]注釈

[編集]- ^ この熱のために4.3GHz以上の速度で高信頼性のCPUを提供するのはほとんど不可能になった。

出典

[編集]- ^ ムーアの法則 考案者が語った長期継続の理由と未来 (日経テクノロジー2015年4月8日掲載)

- ^ Cramming more components onto integrated circuits | 102770822 | Computer History Museum 2020年3月11日閲覧

- ^ “Excerpts from A Conversation with Gordon Moore: Moore's Law” (PDF). Intel Corporation. pp. 1 (2005年). 2012年10月29日時点のオリジナルよりアーカイブ。2006年3月2日閲覧。

- ^ NY Times article 2005年4月17日

- ^ Manek Dubash (2005年4月13日). “Moore's Law is dead, says Gordon Moore”. Techworld. 2006年6月24日閲覧。

- ^ Ray Kurzweil (2001年3月7日). “The Law of Accelerating Returns”. KurzweilAI.net. 2010年6月19日時点のオリジナルよりアーカイブ。2006年6月24日閲覧。

- ^ “Moore's Law at 40 - Happy birthday”. The Economist (2005年3月23日). 2006年6月24日閲覧。

- ^ 半導体開発の「ムーアの法則」は限界かウォール・ストリート・ジャーナル2015年4月18日

- ^ 「ムーアの法則は終わった」、NVIDIAのCEOが言及 EE Times Japan(2017年6月5日)2017年6月5日閲覧

- ^ “Intelが「チックタック」戦略を廃止して3ステージ制を採用、ユーザーへの影響とは?”. GIGAZINE. 2023年4月5日閲覧。

- ^ “ムーアの法則に黄色信号点滅、Intelの10nmプロセス移行の遅れが確実に”. GIGAZINE. 2023年4月5日閲覧。

- ^ “The end of Moore’s Law? Innovation in computer systems continues at a high pace”. 2023年12月9日閲覧。

- ^ Matthew Broersma (2006年6月24日). “Intel, Aberdeen attack AMD speed ratings”. ZDNet UK. 2006年6月24日閲覧。

- ^ “New life for Moores Law”. CNET News.com (2006年4月19日). 2012年7月16日時点のオリジナルよりアーカイブ。2006年6月24日閲覧。

- ^ “Chilly chip shatters speed record”. BBC Online (2006年6月20日). 2006年6月24日閲覧。

- ^ “Georgia Tech/IBM Announce New Chip Speed Record”. Georgia Institute of Technology (2006年6月20日). 2006年6月24日閲覧。